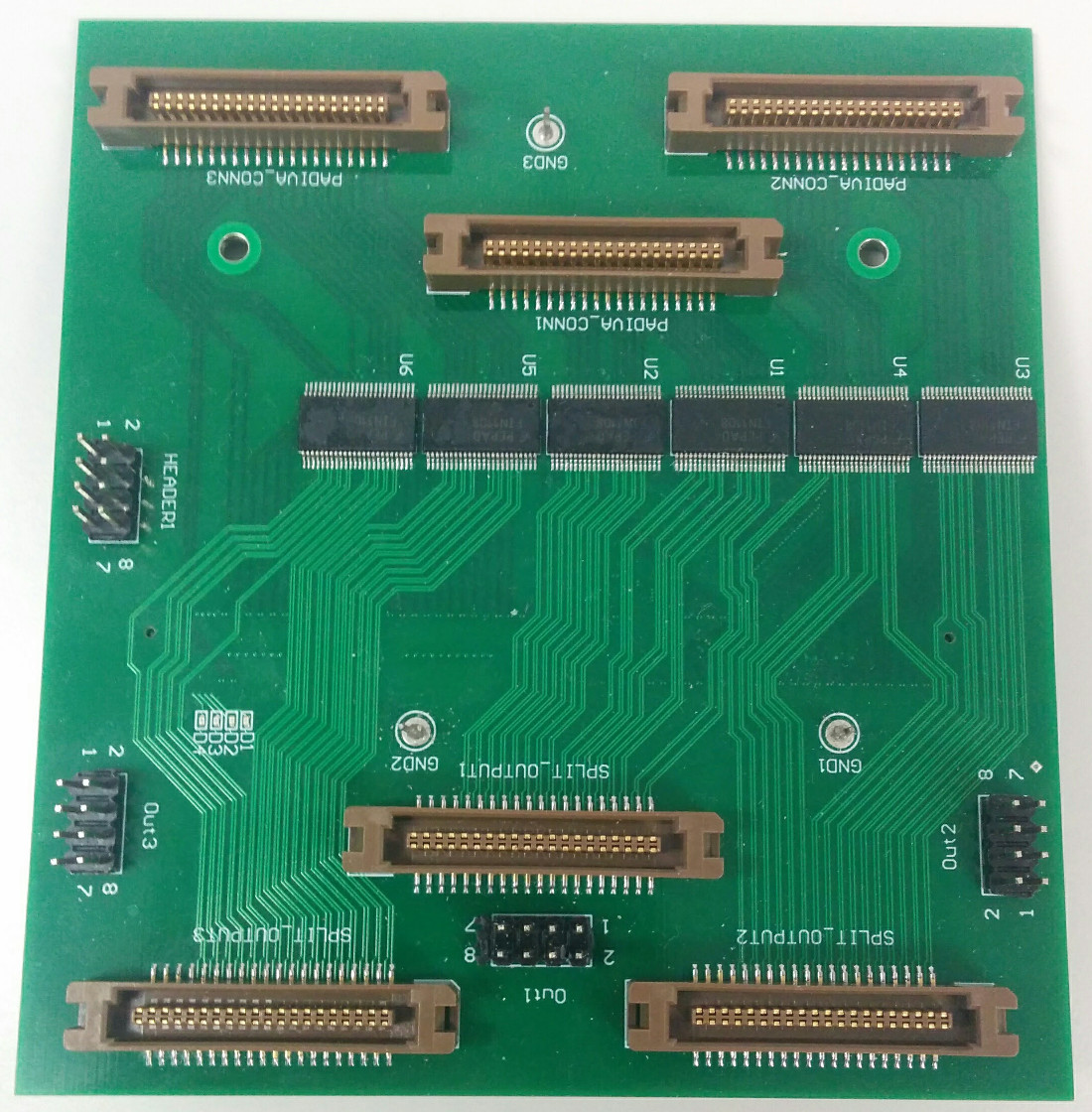

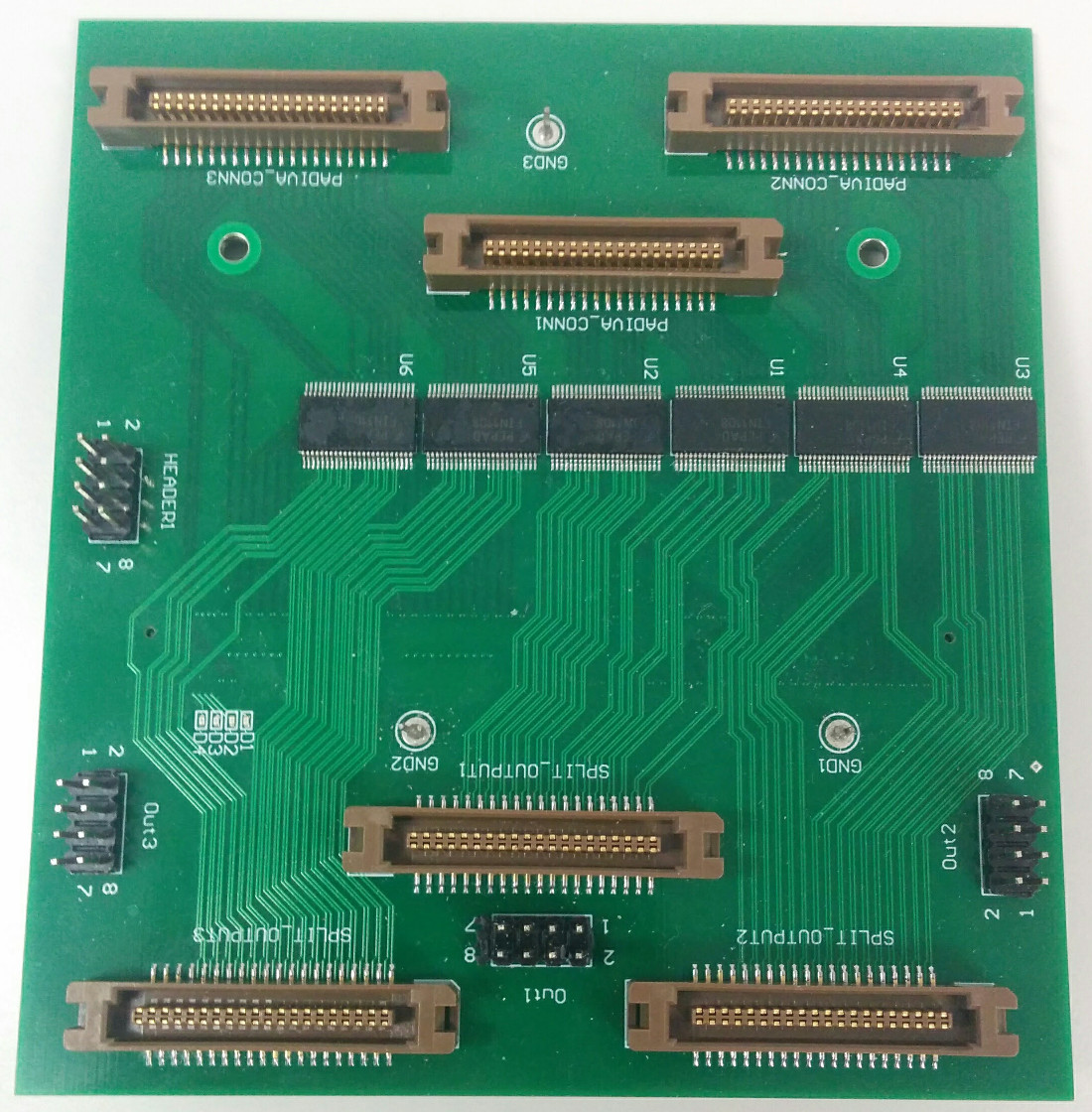

A new adapter AddOn is available, designed by the Krakow group: It features three inputs, identical to those on the 4conn-AddOn to connet Padiwa front-ends. All 48 LVDS input signals are fanned out to a second set of connectors to allow them to be forwarded to another read-out systsm or the CTS.

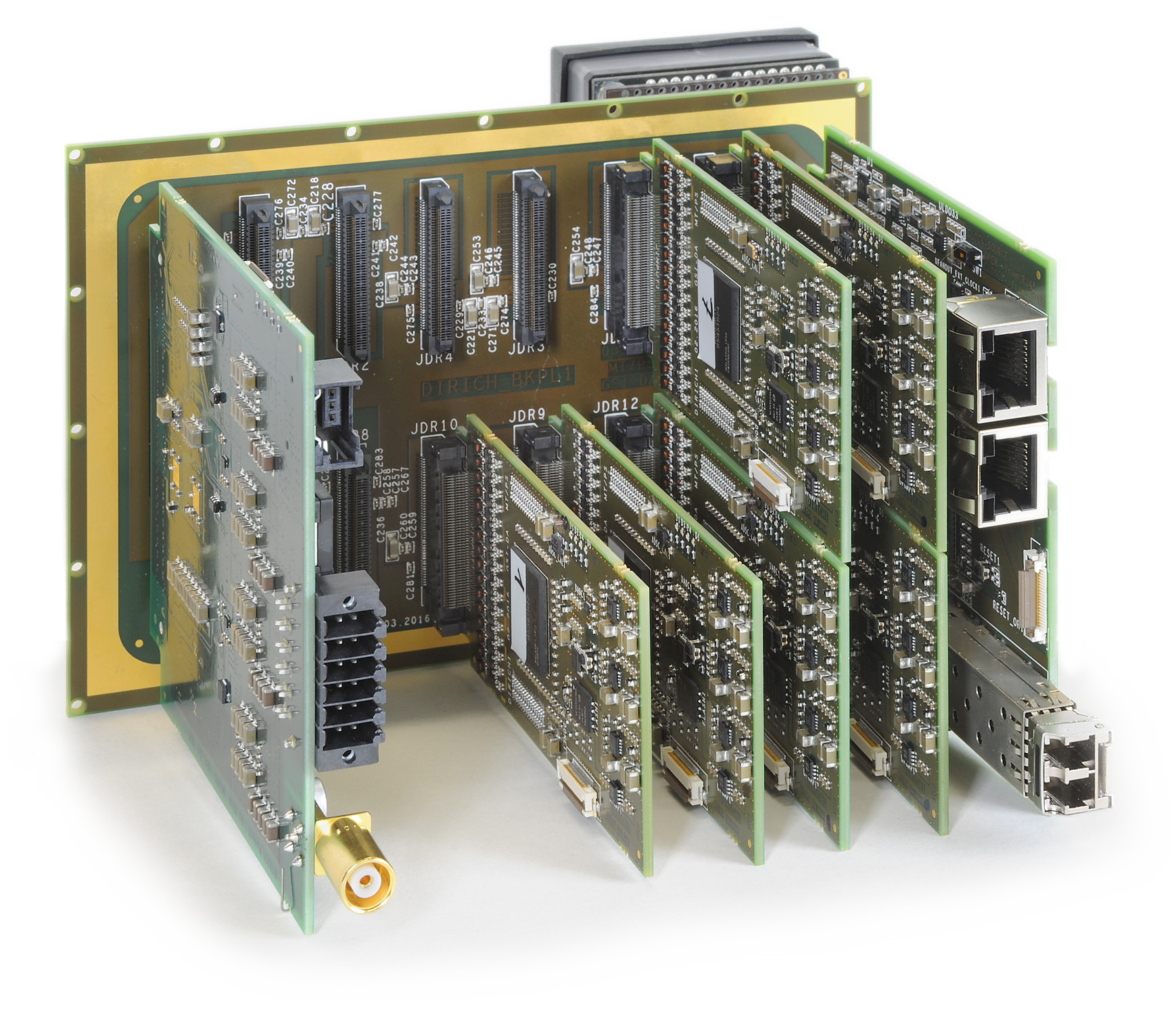

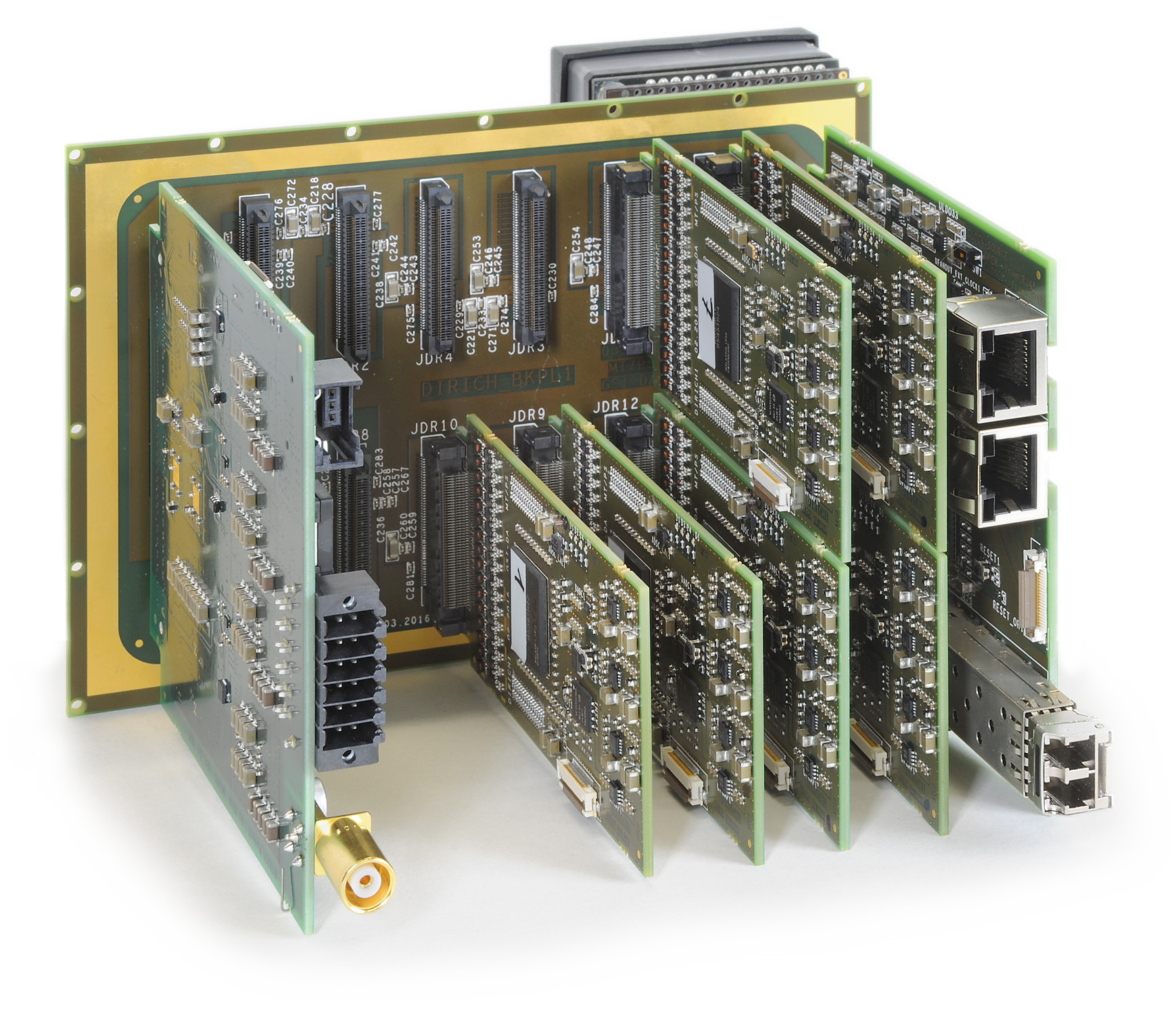

And here it is, the complete module for the Hades and CBM RICH detectors: 6 64-channel MC-PMTs and all electronics for read-out

- The backplane (10x15cm) holds all components. 14 layers in the PCB route all analog and digital signals as well as power

- The power module regulates all necessary supply voltages and provides the HV connection

- The concentrator module connects to the central DAQ and provides trigger and slow-control to all read-out modules

- The DiRich front-end module with in-FPGA TDC and the analog preamplifier stage, see two posts below

An extensive description of the features can be found on a

poster, presented at TWEPP 2016.

Photo: Gabi Otto, GSI

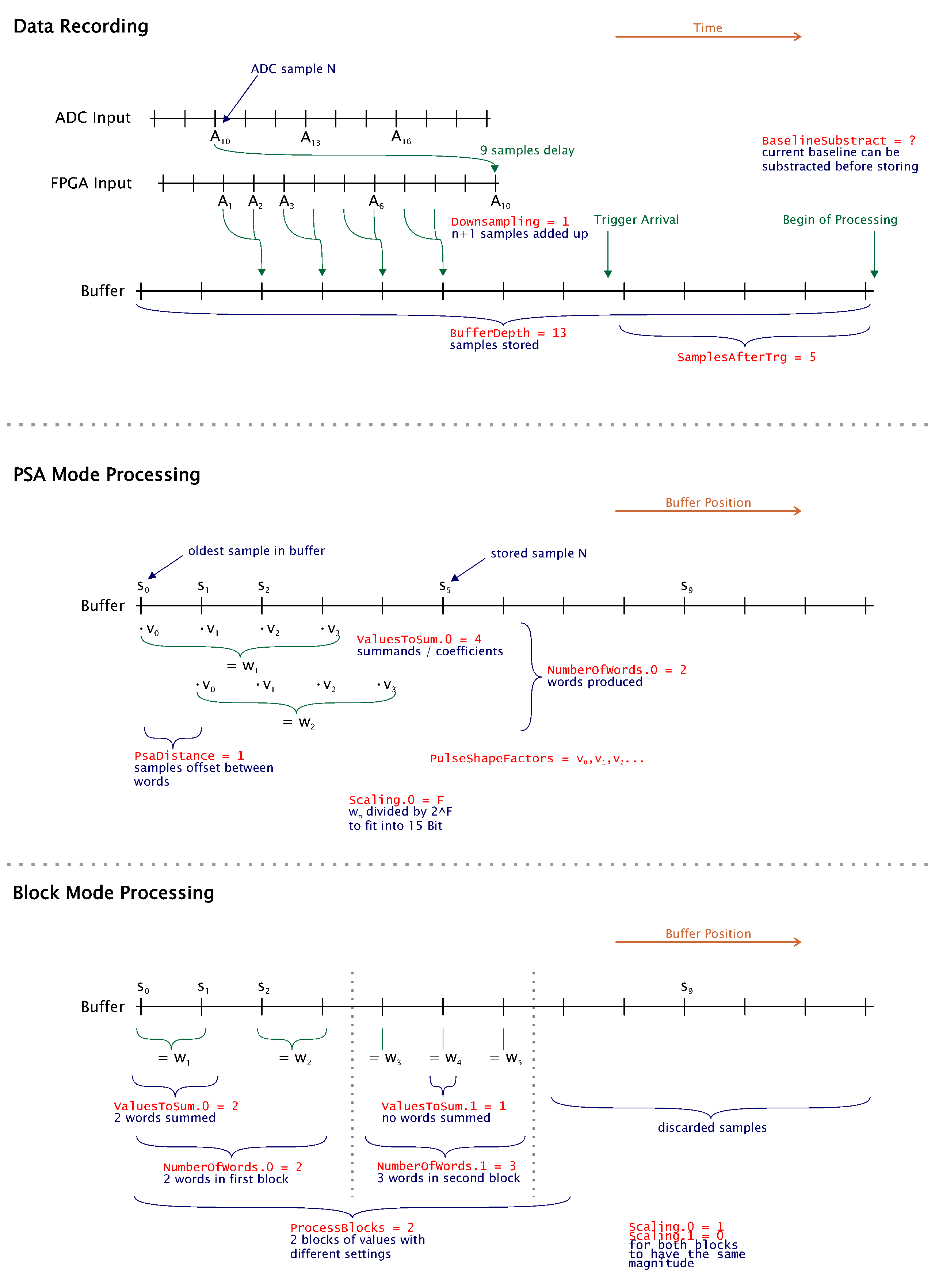

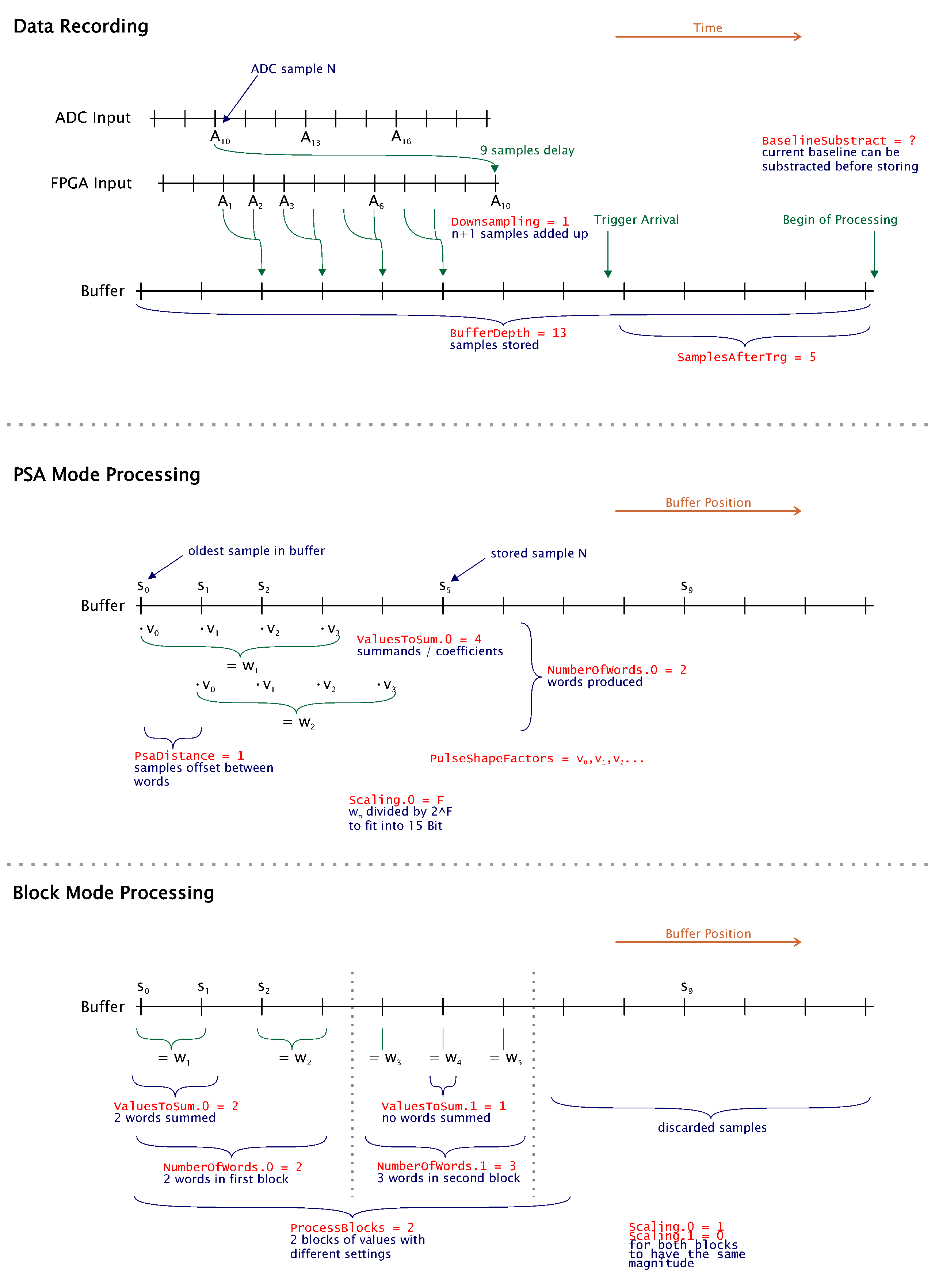

The FPGA firmware to read out our

ADC AddOn has many built-in features:

- Buffer depth, number of words to read-out, downsampling and samples taken after receiving a trigger are configurable

- Trigger Generation - a signal is sent to the CTS if a channel crosses the selected threshold

- Zero Suppression - a signal that did not cross the set threshold during the read-out window is ignored to save bandwidth

- Automatic Baseline calculation, used for the two features mentioned before

- Basic pulse shape analysis is available as well: A set of measured values can be convoluted with a user-defined table of coefficients

Please have a look at the TRB3 Documentation for further details.