Tip of the week: ADC-AddOn Firmware

The FPGA firmware to read out our ADC AddOn has many built-in features:

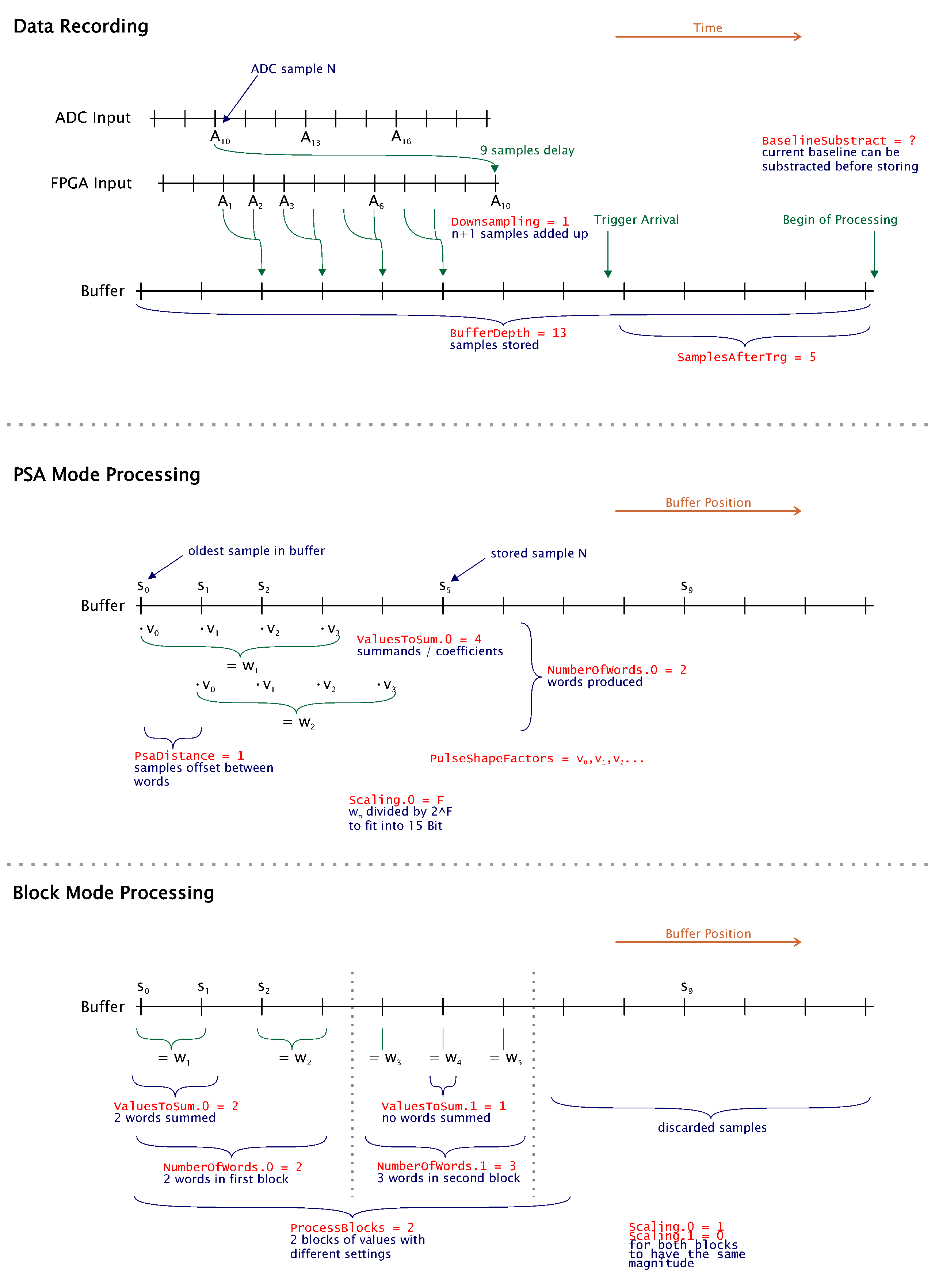

- Buffer depth, number of words to read-out, downsampling and samples taken after receiving a trigger are configurable

- Trigger Generation - a signal is sent to the CTS if a channel crosses the selected threshold

- Zero Suppression - a signal that did not cross the set threshold during the read-out window is ignored to save bandwidth

- Automatic Baseline calculation, used for the two features mentioned before

- Basic pulse shape analysis is available as well: A set of measured values can be convoluted with a user-defined table of coefficients

Please have a look at the TRB3 Documentation for further details.