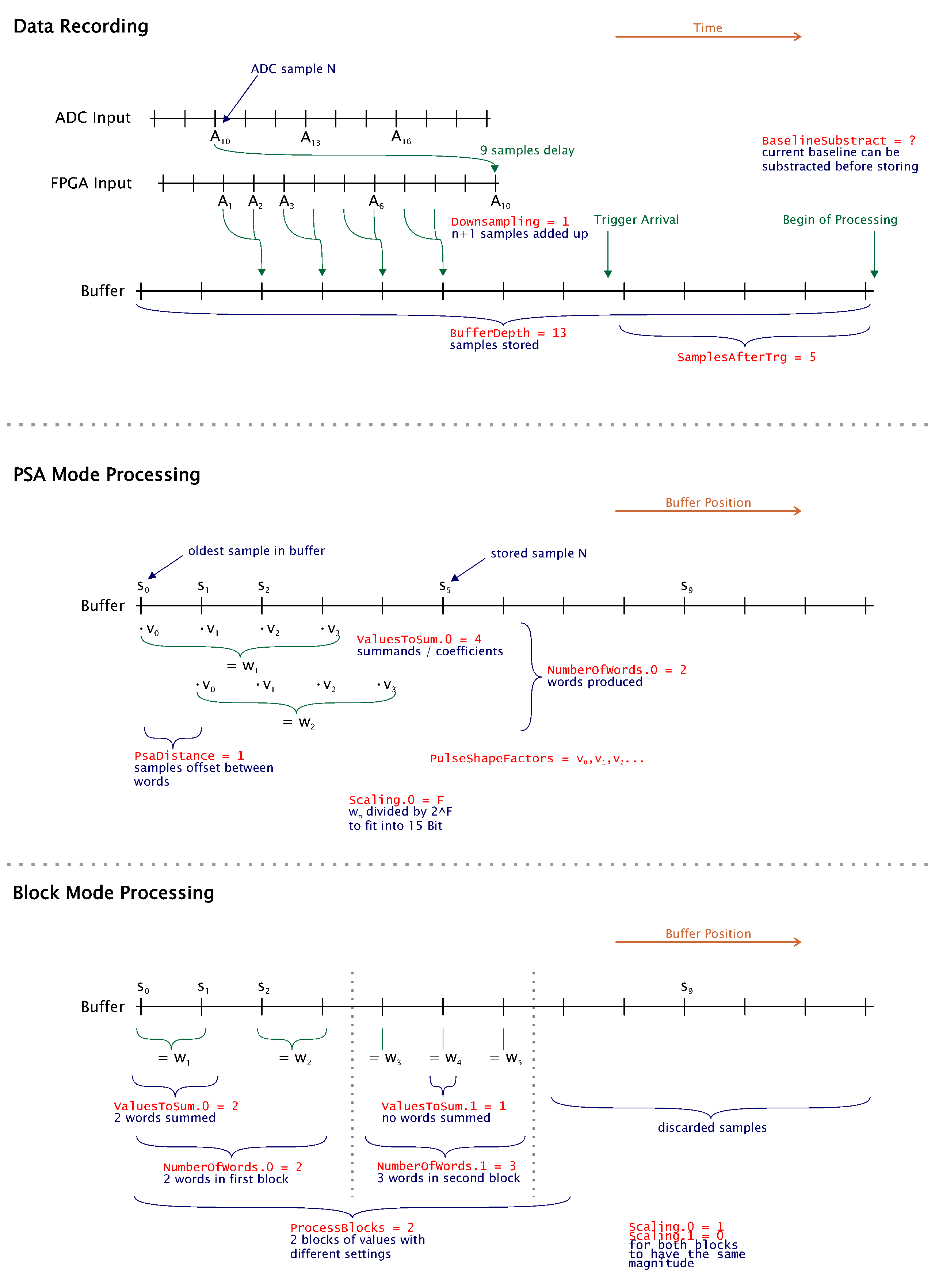

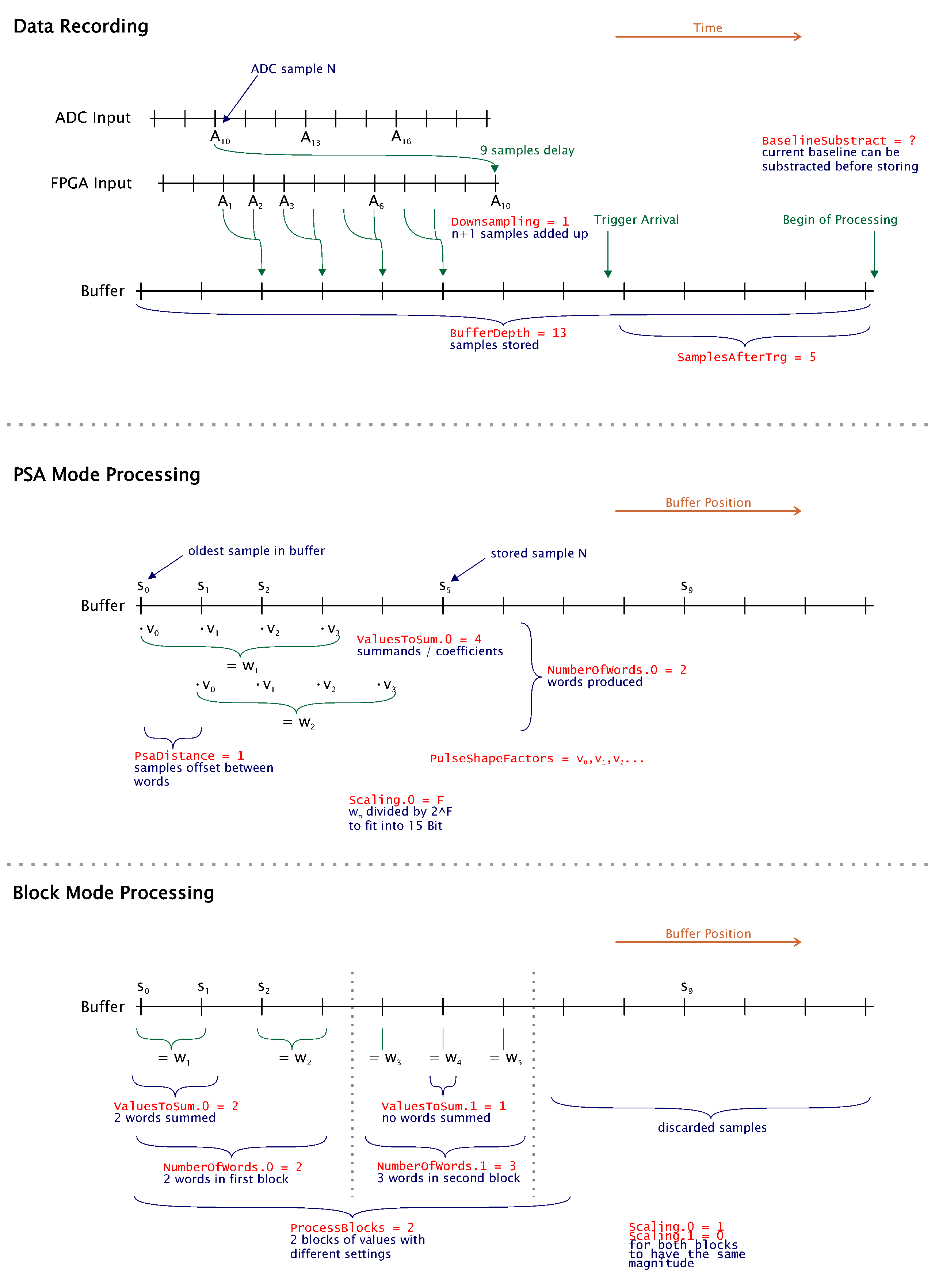

The FPGA firmware to read out our

ADC AddOn has many built-in features:

- Buffer depth, number of words to read-out, downsampling and samples taken after receiving a trigger are configurable

- Trigger Generation - a signal is sent to the CTS if a channel crosses the selected threshold

- Zero Suppression - a signal that did not cross the set threshold during the read-out window is ignored to save bandwidth

- Automatic Baseline calculation, used for the two features mentioned before

- Basic pulse shape analysis is available as well: A set of measured values can be convoluted with a user-defined table of coefficients

Please have a look at the TRB3 Documentation for further details.

The DiRICH module is a 32 channel transformer, amplifier (factor 30), discriminator (with thresholds settings), 😍0ps RMS time precision TDC (currently, can be improved) and finally readout of the data via TRBNet. So, it is an improved version of the combination of a Padiwa + a small part of the TRB3.

The DiRICH module is a 32 channel transformer, amplifier (factor 30), discriminator (with thresholds settings), 😍0ps RMS time precision TDC (currently, can be improved) and finally readout of the data via TRBNet. So, it is an improved version of the combination of a Padiwa + a small part of the TRB3.

The LogicBox provides level conversion and basic logic functions in a small package. As input and output modules two versions each are available: LVDS/TTL on pin-header - four signals in total, either all LVDS or all TTL or mixed. Second option: NIM / TTL on LEMO, three signals in total.

The user can choose between different operating modes: In the basic version, only level conversion is available with limited support for fan-out configuration. There is also an FPGA-AddOn (using a tiny MachXO3 in a 3mm sized package) available - here functions like AND, OR, stretcher, pulser can be selected.

Documentation on the module is available at

this link.

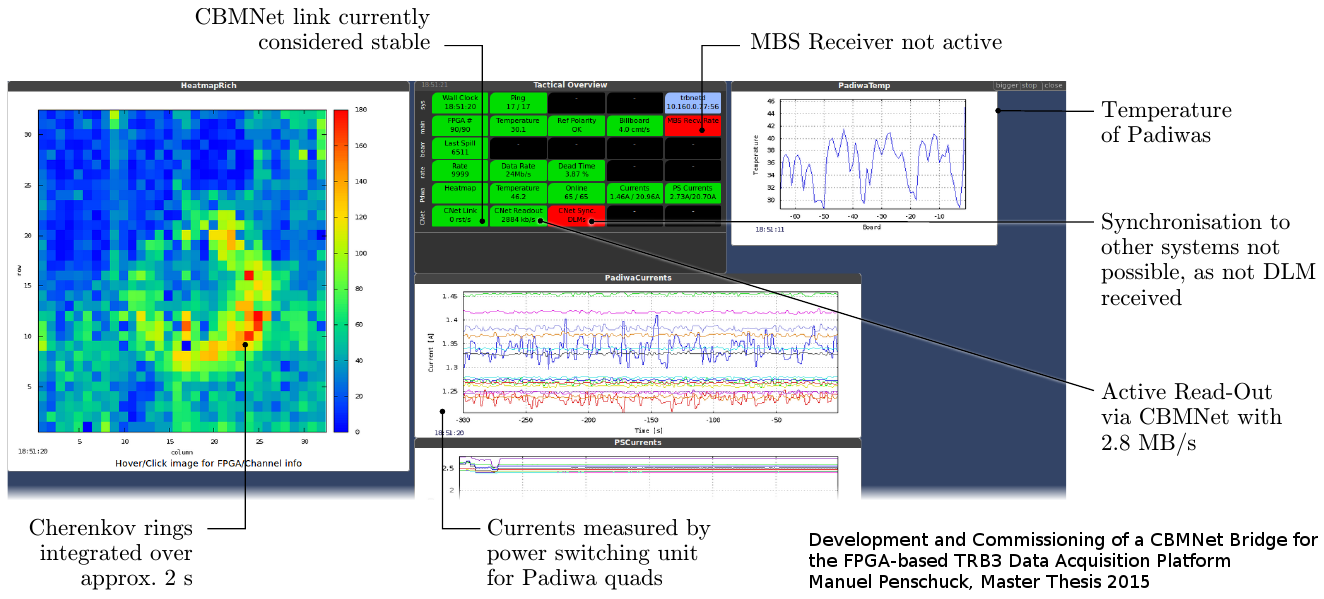

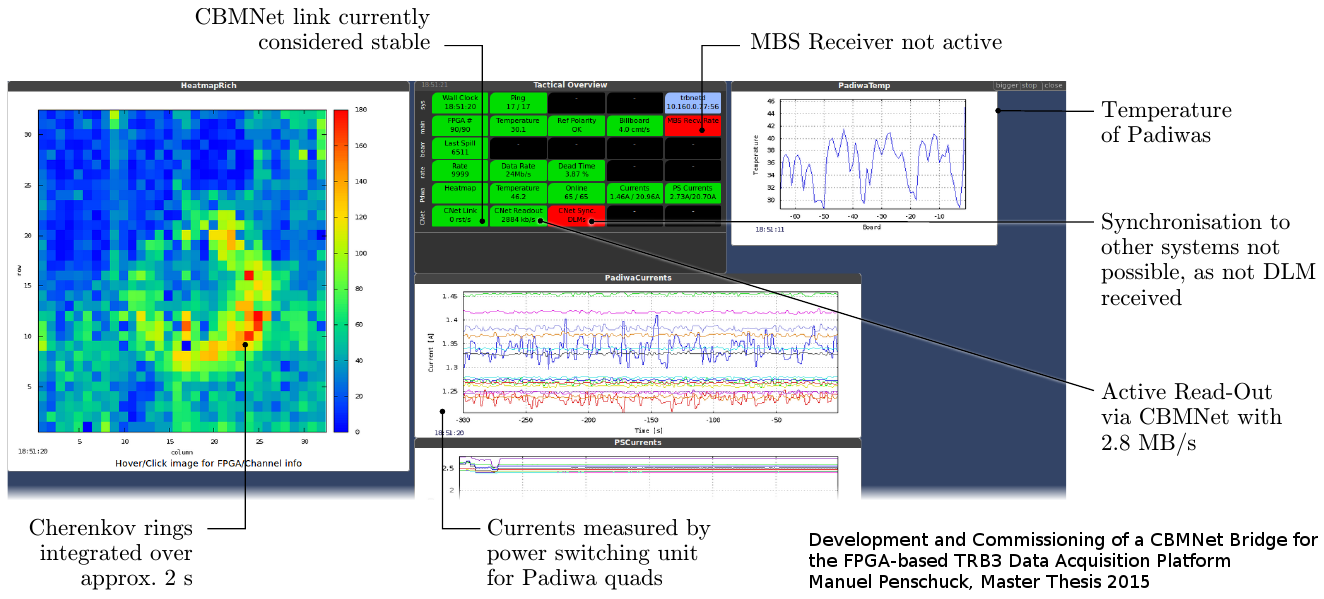

The Dmon tools (available from the daqtools repository) are a set of monitoring scripts that can be adapted to almost any slow control involved in testing a setup. Registers from TrbNet, EPICS variables and information from other sources can be mixed and displayed in graphs and tables. The central part is the "Tactical Overview" showing the current status using a simple color code. Configuration and all monitors are organized in independent script files to facilitate adaption to new applications. All information is accessible from any web browser, including mobile devices.

The recent compile script (trb3/scripts/compile.pl) now accepts the project name as an argument. The FPGA properties and the project path are selected automatically for the project. This property enables parallel compile of the selected projects. Simply edit the compile list in "trb3/scripts/compile_parallel.pl" and run the script. A new tab will be created for each project and the compile will start automatically. For the project settings the "config.vhd" files should be edited individually for each project.

Dependencies: urxvt, tabbedex (https://github.com/michaeltraxler/urxvt-perls/blob/master/tabbedex)

The DiRICH module is a 32 channel transformer, amplifier (factor 30), discriminator (with thresholds settings),

The DiRICH module is a 32 channel transformer, amplifier (factor 30), discriminator (with thresholds settings),